В УЧПУ преобразование информации большого формата производится не дешифрацией одного кода в другой, а методом вычислений с помощью специального процессора. Так, например, в некоторых УЧПУ преобразование двоично-десятичного кода в двоичный и двоичного в десятичный реализуется методом суммирования и вычитания двоичных констант.

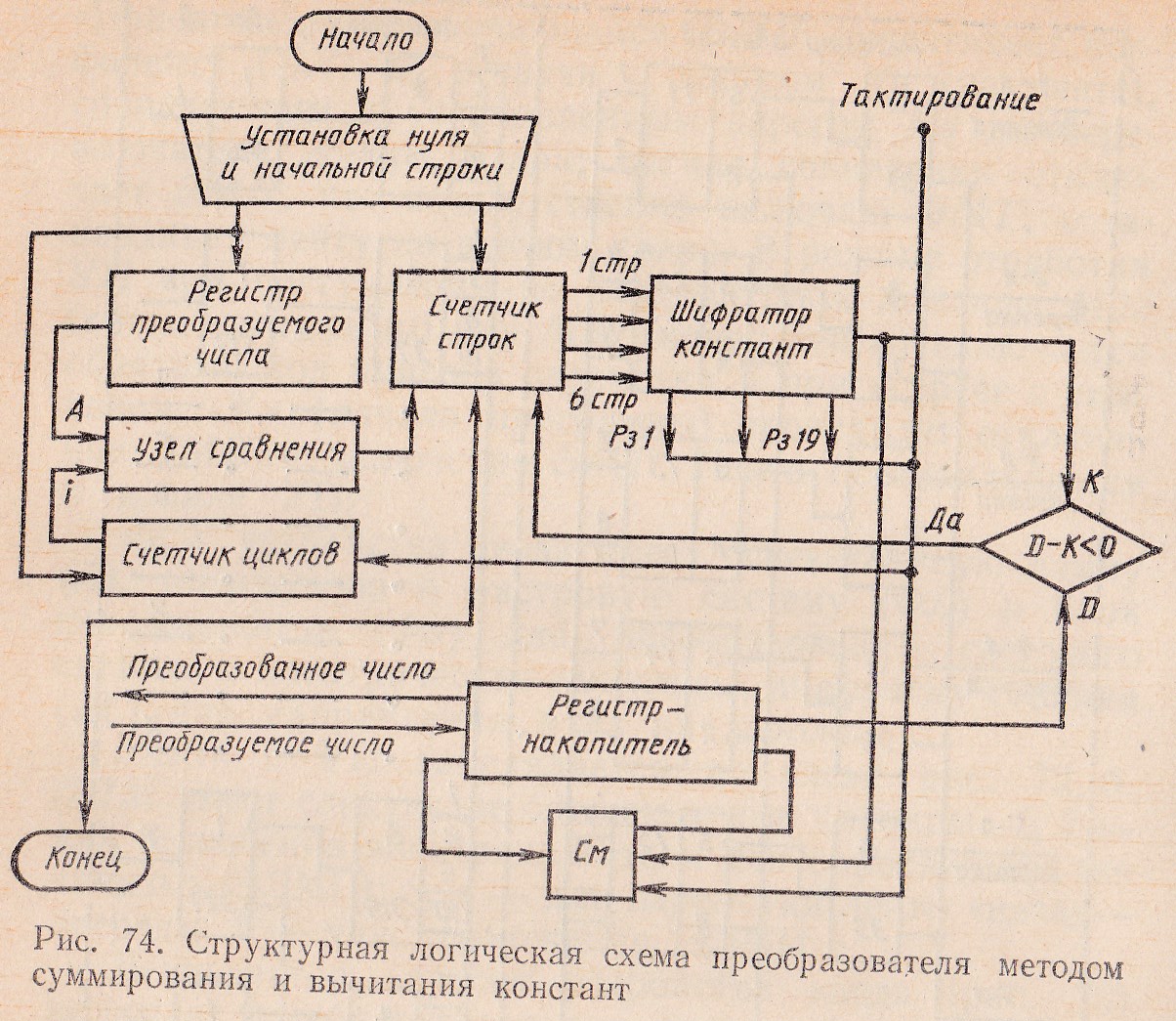

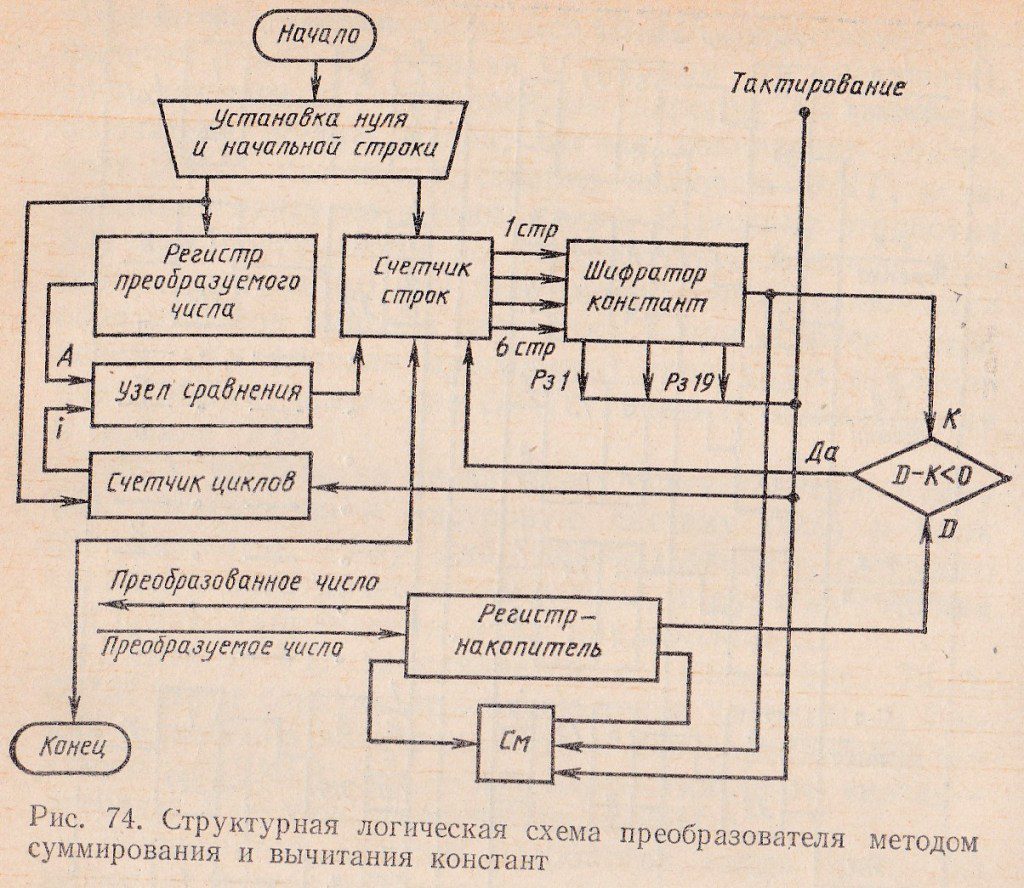

На рис. 74 представлена структурная логическая схема преобразователя, выполняющего преобразование методом суммирования и вычитания констант. Преобразователь включает в себя следующие функциональные узлы:

- регистр преобразуемого числа;

- счетчик циклов, подсчитывающий число циклов суммирований или вычитаний в разряде;

- узел сравнения, который выполняет сравнение состояния счетчика циклов и состояния регистра преобразуемого числа (число суммирований или вычитаний сравнивается с цифрой в данном разряде);

- счетчик строк, подсчитывающий число строк преобразуемого числа и формирующий соответствующую двоичную константу;

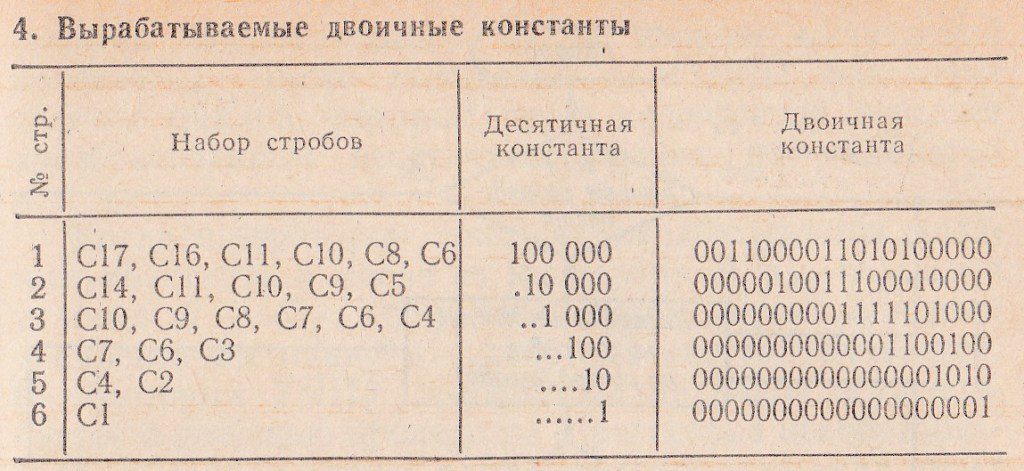

- шифратор констант, обеспечивающий формирование и выдачу двоичной константы Рз1—Рз19 в сумматор (табл. 4);

- узел установки нуля и начальной строки, выполняющий сброс счетчиков в нулевое состояние и установку начальной строки счетчика строк согласно старшему разряду преобразуемого числа;

- сумматор совместно с регистром-накопителем, обеспечивающий суммирование констант и запись накопленной суммы или остатка в регистр-накопитель;

- регистр-накопитель, обеспечивающий хранение преобразованного числа или преобразуемого.

Преобразование кодов в устройстве преобразования происходит по следующему алгоритму. По сигналу «Ввод» счетчик циклов и строк устанавливается в нулевое положение, и число, введенное в регистр числа, устанавливает счетчик строк в состояние начальной строки по старшему разряду введенного числа. С помощью счетчика строк шифратор констант вырабатывает соответствующую двоичную константу (Рз1— Рз19) (см. табл. 4).

В режиме преобразования суммируемая константа будет засылаться в сумматор в каждом цикле, складываться с предыдущим результатом и перезаписываться в регистр-накопитель. Каждый цикл суммирования фиксируется счетчиком циклов, содержание которого сравнивается в схеме сравнения. Если і — А (і— число суммирований констант, А — цифра преобразуемого разряда), то схема сравнения вырабатывает сигнал смены строки. Счетчик строк при смене строки вырабатывает новую константу, и цикл суммирования двоичных констант повторяется, т. е. число суммирований констант в новом разряде также будет равно цифре преобразуемого числа и т. д. Когда счетчик строк установится в нулевое состояние, преобразование прекратится и преобразованное (двоичное) число суммированием констант из регистра-накопителя передается в соответствующий регистр того или иного устройства.

При обратном преобразовании двоичное число засылается в регистр-накопитель и счетчик строк устанавливается в состояние старшей строки. Выработанная константа шифратором констант сравнивается в схеме сравнения с преобразуемым двоичным числом (D). Если D — K <0 (D — преобразуемое двоичное число, К — константа), то происходит переход на новую строку с выработкой младшей константы и т. д. Если D — К≥ 0, то начинается вычитание констант до тех пор, пока не будет выполнено условие D — К <0 (остаток преобразуемого числа меньше вычитаемой константы). Число вычитаний константы фиксирует счетчик циклов, который через дешифратор передает преобразованный десятичный разряд на индикатор и т. д.

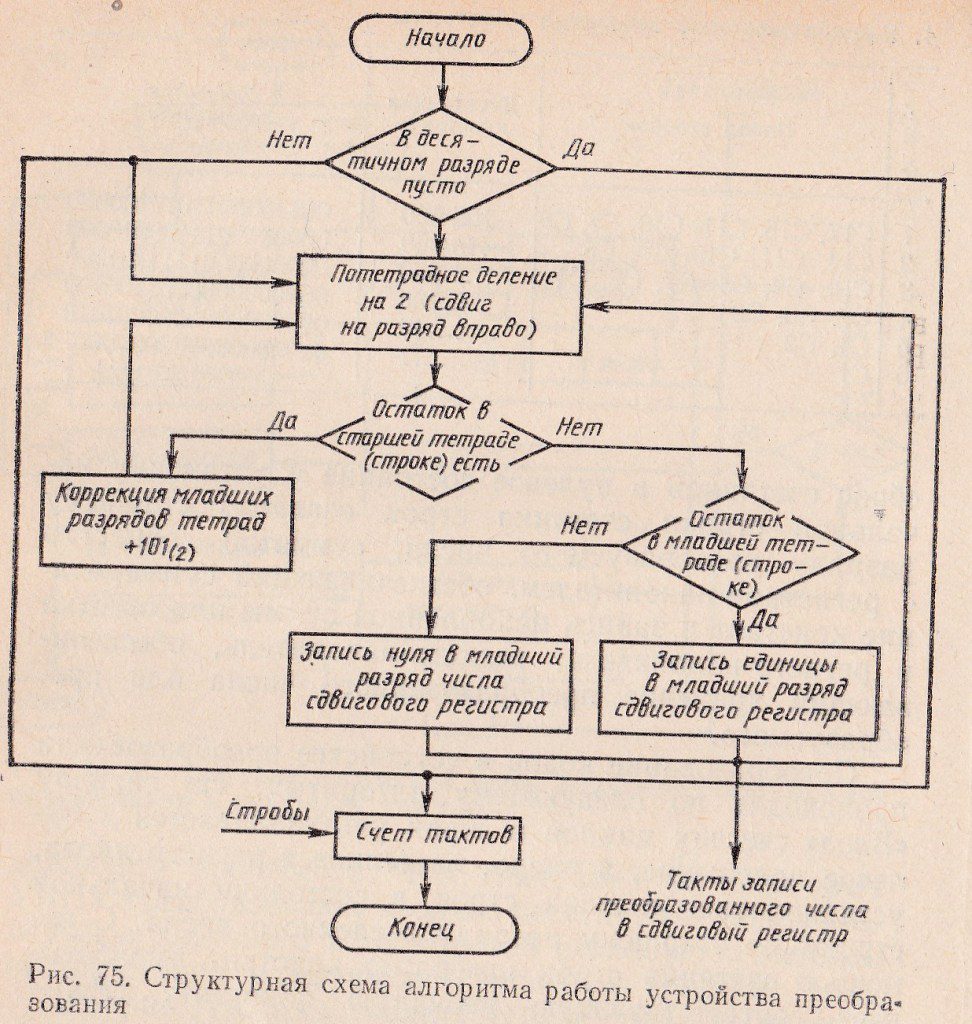

Когда шифратором констант вырабатывается младшая константа и после ее вычитания А раз создается условие Д — К <0, счетчик строк устанавливается в нулевое состояние и преобразование заканчивается. В некоторых УЧПУ преобразование кодов осуществляется с помощью процессора и регистров преобразователя. В данном случае алгоритм преобразования имеет следующее содержание (рис. 75). Введенное двоичное число в сдвиговом регистре (сдвиговый регистр хранит преобразуемое число) потетрадно сдвигается вправо (деление на два). Если в старшем разряде тетрады есть остаток, то тетрада следующего разряда корректируется путем суммирования тетрады с числом пять. Кроме того, если в младшей тетраде есть остаток, то в сдвиговый регистр-накопитель записывается единица и тактом записи производится сдвиг числа в сдвиговом регистре на один разряд. Если в младшей тетраде остатка нет, то в сдвиговом регистре-накопителе тактом записи производится сдвиг только на один разряд. После полного преобразования двоично-десятичного кода счетчик тактов дает сигнал об окончании преобразования и перезаписи преобразованного числа из сдвигового регистра накопителя в соответствующий регистр.

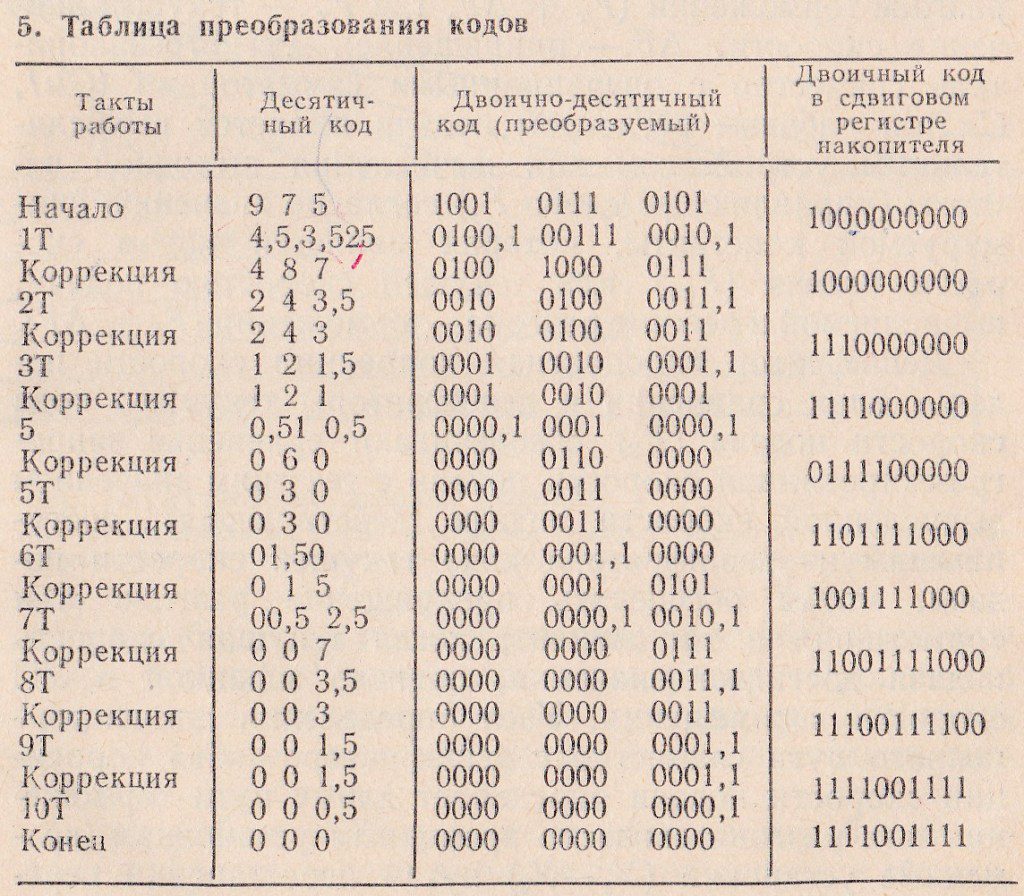

В табл. 5 приведен пример преобразования десятичного числа 975 в двоичное, где указаны действия в каждом такте преобразования и состояние сдвигового регистра накопителя в процессе преобразования.