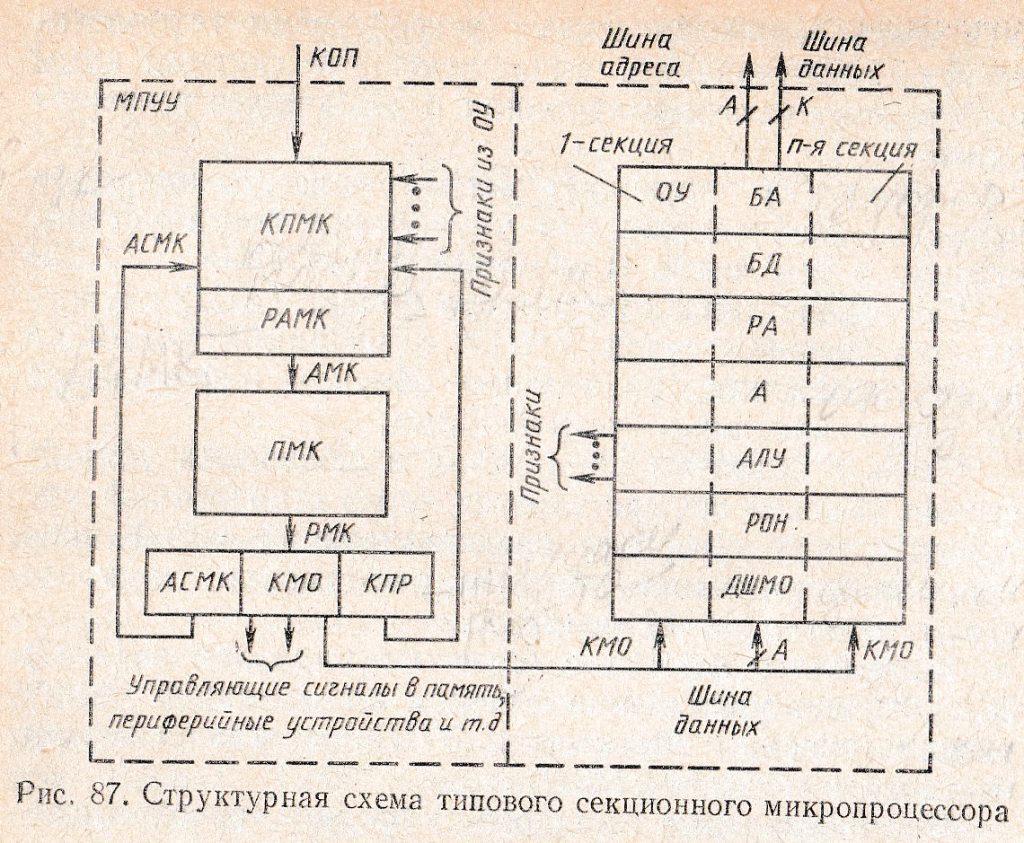

Структурная схема типового секционного микропроцессор УЧПУ показана на рис. 87. МП состоит из двух функциональных модулей: микропрограммного устройства управления (МПУУ) и операционного устройства (ОУ), построенного из отдельных секций. МПУУ включает в себя:

- память микрокоманд (ПМК), которая предназначена для хранения принимаемых команд;

- контроллер последовательности микрокоманд (КПМК), основным назначением которого является реализация управляющих структур (фрагментов), встречающихся в микрокомандах.

Таким образом контроллер обеспечивает дешифрацию кода операции команды для обращения к первой микрокоманде микропрограммы, формирует адреса следующих микрокоманд как линейной последовательности, так и условных или безусловных переходов к микропрограмме. Кроме того, некоторые контроллеры могут хранить признак переходов, управлять прерываниями на микропрограммном уровне. Как правило, в комплект микропроцессора входят модули контроллеров последовательности микрокоманд для организации управления в различных режимах.

МПУУ работает следующим образом. Код операции (КОП) с регистра команд поступает на вход контроллера последовательности микрокоманд (КПМК), и на выходе регистра адреса микрокоманды (РАМК) контроллера формируется адрес первой микрокоманды (АМК) выполняемой микропрограммы. Микрокоманда, подлежащая реализации в текущем микрокомандном цикле, считывается из памяти в регистры микрокоманд (РМК). Микрокоманда содержит три основных поля, содержание которых хранится в соответствующих узлах:

- поле кода микрооперации (КМО), определяющее вид операции, выполняемой одним из устройств микро-ЭВМ;

- поле, в котором закодированы признаки результата (КПР), поступающие из ОУ в контроллер и анализируемые контроллером при выполнении команд условного перехода по данным признакам условия;

- поле, в котором содержится код адреса для формирования адреса следующей команды (АСМК).

После выполнения считанной микрокоманды цикл повторяется. Управляющие сигналы микрокоманд подаются в соответствующие устройства микроЭВМ.

ОУ предназначено для выполнения всех арифметических и логических операций. ОУ собирают из секций процессорных элементов, каждый из которых содержит арифметико-логическое устройство (АЛУ), регистры общего назначения (РОН), аккумулятор (А) — накапливающий регистр, дешифратор микрооперации (ДШМО), буфер данных (БД) и буфер адреса (ВА), позволяющие временно хранить адрес (А) и данные (К).

Одной из особенностей ОУ является вертикальное разбиение, что требует меньшего числа передач кодов между отдельными БИС. Шины данных, шины адреса и кода микроопераций объединяются в общую магистраль. Основными достоинствами секционных МП являются возможность разработки микроЭВМ с максимальным соответствием структуре характеризуемых задач, исключение избыточности структуры и разрядов, выбор произвольной нестандартной разрядности. Наличие независимых адресных шин и шин входных и выходных данных (шины адресов и данных могут быть различных форматов) позволяет организовать сопряжение с памятью и периферийными устройствами без использования мультиплексирования.