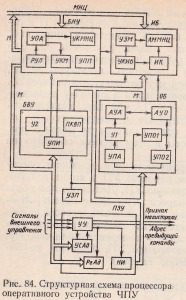

На рис. 84 показана типовая структурная схема процессора оперативного УЧПУ, в который входят несколько блоков. Оперативный блок (ОБ) предназначен для вычисления адресов команд и выполнения арифметико-логических действий над операндами. Оперативный блок включает в себя шестнадцатиразрядное арифметическое устройство обработки адресов (АУА), арифметическое устройство операндов (АУО), адресную микропрограммную управляющую память (УПА), микропрограммные управляющие оперативные памяти (УПО1, УПО2) и узел управления (У1), который осуществляет синхронизацию работы узлов ОБ. В ОБ для обмена информацией предусмотрена четырехканальная внутренняя магистраль связи, где М (15—0) соединяет АУА и АУО с выходными регистрами УПА, УП01, УП02; вторая магистраль соединяет выходные магистральные регистры УПА, АУА с другими устройствами; выходные магистральные регистры УП01, УП02 подключены к третьей магистрали; четвертая магистраль используется для организации ветвлений по признакам (условиям).

На рис. 84 показана типовая структурная схема процессора оперативного УЧПУ, в который входят несколько блоков. Оперативный блок (ОБ) предназначен для вычисления адресов команд и выполнения арифметико-логических действий над операндами. Оперативный блок включает в себя шестнадцатиразрядное арифметическое устройство обработки адресов (АУА), арифметическое устройство операндов (АУО), адресную микропрограммную управляющую память (УПА), микропрограммные управляющие оперативные памяти (УПО1, УПО2) и узел управления (У1), который осуществляет синхронизацию работы узлов ОБ. В ОБ для обмена информацией предусмотрена четырехканальная внутренняя магистраль связи, где М (15—0) соединяет АУА и АУО с выходными регистрами УПА, УП01, УП02; вторая магистраль соединяет выходные магистральные регистры УПА, АУА с другими устройствами; выходные магистральные регистры УП01, УП02 подключены к третьей магистрали; четвертая магистраль используется для организации ветвлений по признакам (условиям).

Блок внутреннего управления (БВУ) служит для управления обменом по внутренней магистрали М процессора, управления интерфейсным блоком при обмене информацией между внутренней магистралью и общей (МНЦ), управления совместно с блоком наружного управления (БНУ) обменом информацией с индикацией и с другими активными блоками, а также управления процедурами прерываний. БВУ включает в себя следующие узлы: микропрограммную управляющую память внутрипроцессорного интерфейса (УПИ), узел формирования псевдокоманд и векторов прерывания (ПКВП), узел управления данным блоком (У2).

Интерфейсный блок (ИБ) предназначен для установления порядка (дисциплины) обмена по магистрали МНЦ, информационной связи процессора с другими устройствами УЧПУ. Блок включает следующие узлы:

- узел арбитра магистрали (АММНЦ), которая устанавливает приоритетную дисциплину обмена;

- узел захвата магистрали (УЗМ), выполняющий запрос на использование магистрали обмена;

- узел информационного коммутатора обмена (НК) для управления селекционным режимом обмена между узлами;

- узел формирования сигналов управления и сигналов идентификаторов обмена для интерфейсного обмена с магистралью (УКИБ).

Блок наружного управления (БНУ) предназначен для управления обменом при обращении к процессору по системным адресам, смены режимов работы процессора по запросам, управления структурными элементами при выполнении процедур прерываний, формирования признаков внешних запросов на прерывание. Блок наружного управления включает в себя следующие узлы: узел опознания адреса процедуры (УОА), узел формирования сигналов квитирования (УКМНЦ) для обмена информацией по магистрали МНЦ, регистры с управляющей логикой (РУЛ) для обмена информацией между магистралью М и общей магистралью МНЦ, узел контроля магистрали (УКМ), узел формирования признаков прерываний (УПП).

Постоянное запоминающее устройство (ПЗУ) предназначено для хранения постоянных команд, констант, процедур (циклов) и т. д. ПЗУ включает в себя следующие узлы:

- узел управления (УУ), который обеспечивает управление данным блоком при выборке информации;

- узел сравнения адресов (УСАд), который обеспечивает сравнение адресов запроса с адресами при выборке;

- регистры адресов (РгАд) для записи запрашиваемого адреса;

- накопитель информации (НИ), представляющий собой группу ячеек с определенным адресным пространством, узел запуска процессора (УЗП).

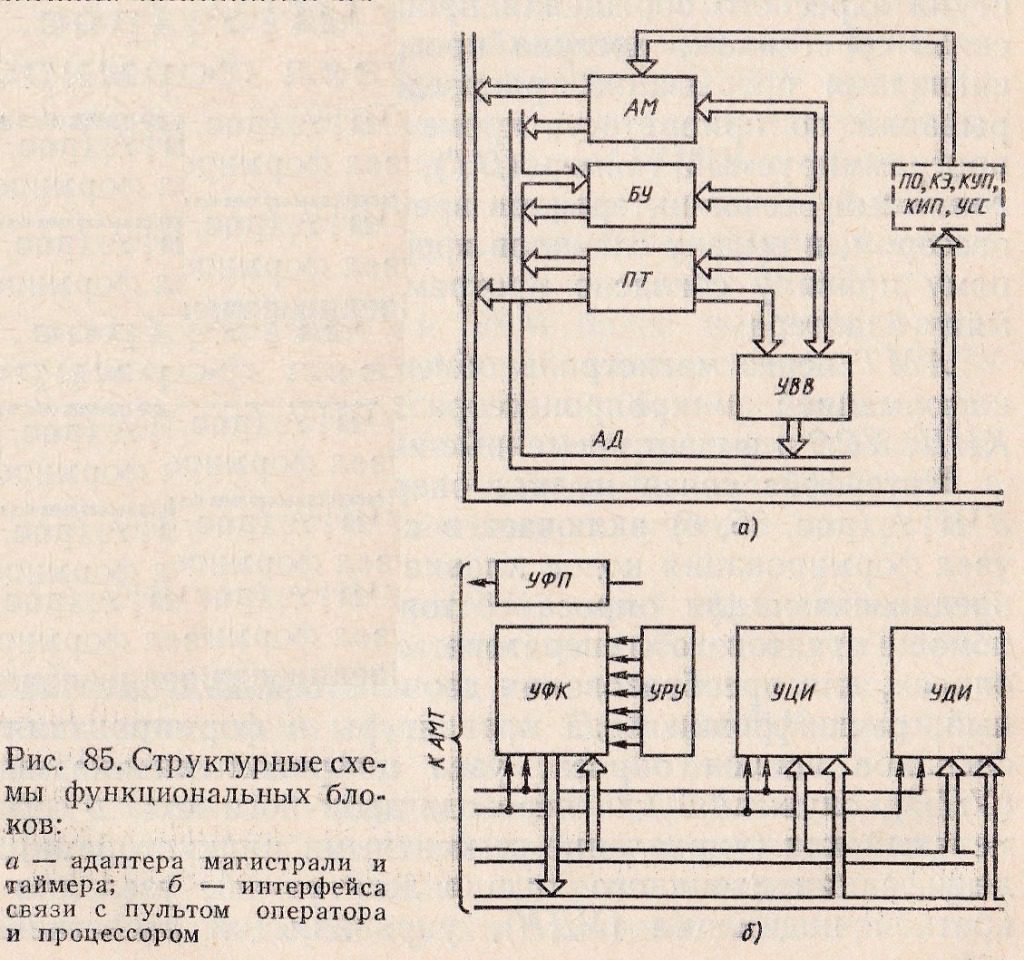

Адаптер магистрали и таймер (АМТ) (рис. 85, а), служат для управления обмена данными между процессором и устройствами связи с объектом управления (станком), которые подключены к общей магистрали МНЦ и имеют интерфейс, отличный от интерфейса самого УЧПУ. Таймер, входящий в ячейку AMT, предназначен для отсчета интервалов времени, программно задаваемых процессором в виде двоичного кода, выдачи этих сигналов по определенному правилу и выдачи сигнала прерывания на процессор по запросам.

Адаптер магистрали и таймер (АМТ) (рис. 85, а), служат для управления обмена данными между процессором и устройствами связи с объектом управления (станком), которые подключены к общей магистрали МНЦ и имеют интерфейс, отличный от интерфейса самого УЧПУ. Таймер, входящий в ячейку AMT, предназначен для отсчета интервалов времени, программно задаваемых процессором в виде двоичного кода, выдачи этих сигналов по определенному правилу и выдачи сигнала прерывания на процессор по запросам.

Адаптер магистрали и таймер включают в себя следующие узлы:

- узел ввода-вывода (УВВ), предназначенный для ввода адресной информации с линией АД (адресная магистраль) в устройство AMT и выдачи данных, поступающих от схемы счетчиков на шины АД (шаги переадресации);

- блок управления (БУ), предназначенный для формирования и распределения сигналов управления по устройствам AMT, а также для формирования сигнала ответа о готовности на ввод;

- адаптер магистрали (AM) осуществляет реализацию доступа адресного обращения процессора к устройствам связи со станком;

- доступа программного управления сигналами прерываний, распределение сигналов прерываний по приоритету;

- кроме того, в AMT входит программируемый таймер (ПТ), обеспечивающий программный отсчет интервалов времени, задаваемых процессором, и выдачу сигналов прерываний по определенному правилу согласно программе, записанной в памяти адаптера.

AMT через магистраль обмена управляет обменом информацией микропроцессора с МО, КЭ, КУП, КИП, УСС и выдает временные интервалы управления.

Интерфейс связи пульта оператора с процессором УЧПУ (рис. 85, б) включает в себя следующие узлы: узел формирования кодов клавиатуры (УФК), который предназначен для опроса состояния клавиатуры при помощи тактового генератора с записью состояния опроса, для преобразования двоичного кода в десятичный, расшифровки кода клавиатуры и формирования сигналов записи опроса; узел цифровой индикации (УЦП), служащий для перевода двоичного кода в сегментный код (управление сегментными индикаторами), дешифрации двоичного кода в десятичный; узел дискретной индикации (УДИ), управляющий засветкой контрольных ламп, индикаторов и транспарантов; узел формирования сигналов признака (УФП), предназначенный для управления сигналами контрольных ламп, которые подтверждают наличие задействованных клавиш (режимов) или отмену их действия; узел ручного управления (УРУ), служащий для формирования кодов при нажатии на клавиши ручного управления.