Состав и особенности схем ФСУ зависят от следующих основных факторов: закона распределения квантов энергии по тактам интервала ТП; видов представления сигналов регулирования N ± N0. C; степени централизации использования ФСУ; функционального состава используемой для ФСУ элементной базы. На основании этих факторов по принципу функционирования ФСУ можно разделить на три класса:

- ФСУ с параллельно-последовательным преобразованием сигнала регулирования N ± N C (сигнал управления), который может быть реализован на преобразователях кодов с применением ПЗУ или комбинированной схемы, а также на генераторах весовых последовательностей с применением двоичного или десятичного умножителя весов, с применением вычислителя соотношений М и N ± N0. C, где М характеризует длительность интервала Т по числу разрядов;

- ФСУ с последовательным преобразованием сигнала управления N ± N C, которое может быть реализовано на универсальных вычислителях с применением накапливающего или сдвигового регистра;

- ФСУ с программируемой диодной матрицей.

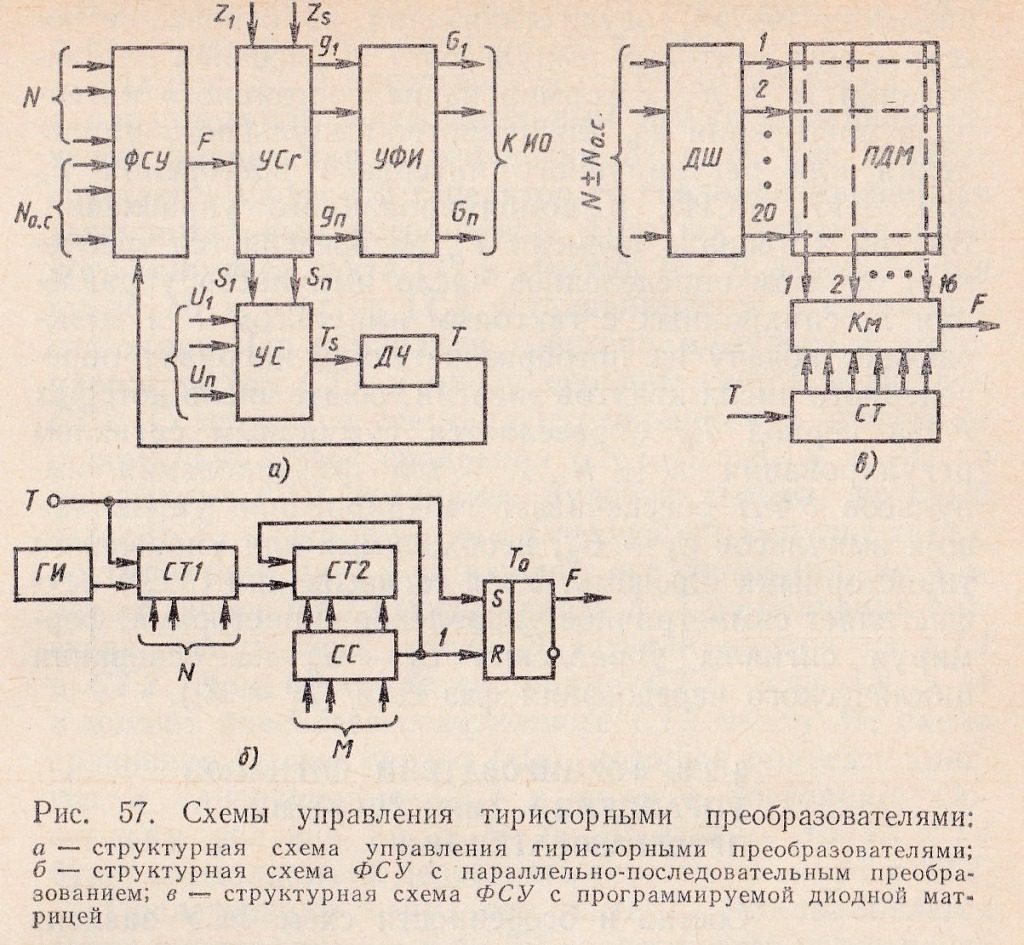

На рис. 57, 6 представлена структурная схема ФСУ с параллельно-последовательным преобразованием методом вычисления соотношения М и N, где в схеме сочетается цифровой генератор со специализированным вычислительным устройством. При поступлении каждого импульса такта (Т) в счетчик (СТ1) записывается число N, а триггер (Т0) устанавливается в единичное состояние. По окончании действия импульса Т отпирается выход СТ1 и число переписывается в счетчик СТ2. Содержимое счетчика сравнивается с числом М с помощью схемы сравнения (СС). Если N <М, то на выходе СТ2 возникает нулевой сигнал, который оставит T0 в состоянии «1». Следующий импульс такта, поступающий на T0, не изменит его состояния, но разрешит запись в СТ1 нового числа N. По окончании действия импульса Т число N переписывается из СТ1 в СТ2. При проверке состояния СТ2, если 2N> М в момент равенства содержимого СТ2 числу М, схема сравнения выдает сигнал («1»), который приведет триггер и одновременно СТ2 в нулевое состояние. Поскольку условие 2N> М не нарушено, то из СТ1 будет продолжаться перезапись остатка 2N — М в СТ2.

Последующим импульсом такта Т0 устанавливается снова в состояние «1» и в СТ1 записывается новое число N с последующей перезаписью в СТ2. Если N + (2N —М) ≥ М, то Т0 установится в нулевое положение с помощью сигнала сравнения и с помощью этого сигнала происходит установка в ноль СТ2, т. е. цикл повторяется с выдачей числа F. Если N + (2N — М) <М, то на выходе схемы сравнения будет «0» и Т0 останется в прежнем состоянии «1», что вызовет засылку и перезапись нового числа N из СТ1 в СТ2 с последующей проверкой. Таким образом, число F, определяющее действие временного интервала, зависит от суммированной константы (время интервала F определяется включением и отключением T0).

Формирователи сигналов управления на основе преобразователей кодов относятся к группе схем с параллельно-последовательным и последовательным преобразованием сигналов регулирования N в управляющее слово F. Они характеризуются широкими функциональными возможностями и высоким быстродействием. Широкие функциональные возможности заключаются в реализации одной структуры ФСУ любого способа импульсного управления, поскольку создание способа происходит на этапе проектирования устройства на запоминающее устройство типа ОЗУ, ПЗУ, ППЗУ. Высокое быстродействие определяется отсутствием вычислительных устройств. В зависимости от преобразования кода N в слово F рассматриваемые ФСУ можно разделить на устройства с логическим преобразователем комбинированного типа и устройства с ЗУ, в котором записана программа преобразования (преобразователь типа микроконтроллера).

В первом случае способ распределения N единиц по М разрядам слова F построен введением в логическую структуру преобразователя схемы с определенными соединениями элементов на основании логических функций преобразования. Во втором случае функция преобразования заносится в ЗУ, причем адресом выборки слова F является код N. В зависимости от вида ЗУ ФСУ могут быть узконаправленными (используется ПЗУ), перепрограммируемыми (используется ППЗУ) или оперативными (в качестве ЗУ используется память микроЭВМ). Использованная память микроЭВМ не требует дополнительного процессора для обработки информации программы ФСУ.

На рис. 57, в показана структурная схема ФСУ с программируемой диодной матрицей (ПДМ). ПДМ имеет двадцать горизонтальных и шестнадцать вертикальных шин, т. е. емкость 20X16 = 320 битов на одну плату. Кроме того, на каждую матрицу требуется один дешифратор (ДШ) кода N ± N0. C для распределения данного кода по двадцати шинам матрицы. Формирование слова F осуществляется при условии ТП ≤16Т. При большей разрядности входного слова или длительности ТП необходимо наращивать схему ПДМ дополнительными матрицами. При подаче кода N ± N0. C, с производится его дешифрация с помощью матрицы, где составные части слова сформируют выходные сигналы на матрице (согласно распайке диодов). Выходные сигналы ПДМ и тактовые сигналы, поданные на коммутатор Км, сформируют слово F из отдельных весовых единиц. Данное число F, сформированное импульсным счетчиком (СТ), и определит число квантов энергии, подаваемых в нагрузку согласно кодовому числу N ± N0. C.